# IMAGE SENSORS

# DATA SHEET FTT1010-M Frame Transfer CCD Image Sensor

Product specification File under Image Sensors 2002 July 10

# FTT1010-M

- 1-inch optical format

- 1M active pixels (1024H x 1024V)

- Progressive scan

- Excellent anti-blooming

- Variable electronic shuttering

- Square pixel structure

- H and V binning

- 100% optical fill factor

- High dynamic range (>72dB)

- High sensitivity

- · Low dark current and fixed pattern noise

- Low read-out noise

- Data rate up to 2 x 40 MHz

- Mirrored and split read-out

#### Description

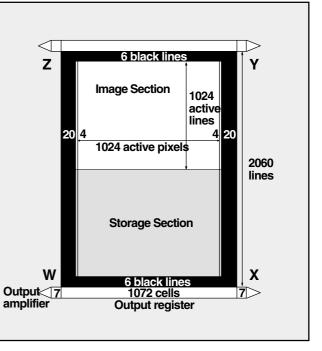

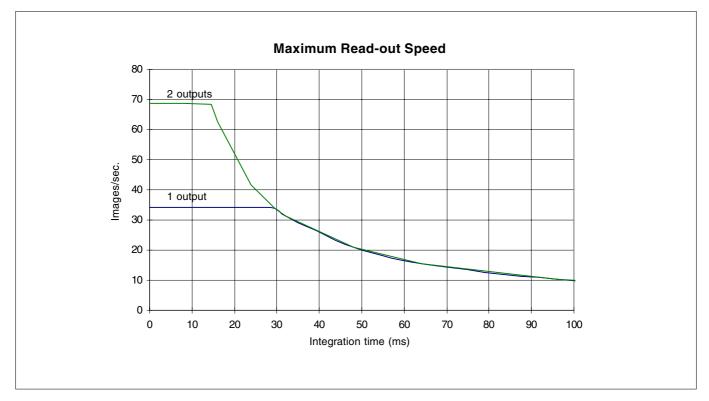

The FTT 1010-M is a monochrome progressive-scan frame-transfer image sensor offering  $1K \times 1K$  pixels at 30 frames per second through a single output buffer. The combination of high speed and a high linear dynamic range (>12 true bits at room temperature without cooling) makes this device the perfect solution for high-end real time medical X-ray, scientific and industrial applications. A second output can either be used for mirrored images, or can be read out simultaneously with the other output to double the frame rate. The device structure is shown in figure 1.

#### **Device structure**

| Optical size:         | 12.288 mm (H) x 12.288 mm (V) |

|-----------------------|-------------------------------|

| Chip size:            | 14.572 mm (H) x 26.508 mm (V) |

| Pixel size:           | 12 μm x 12 μm                 |

| Active pixels:        | 1024 (H) x 1024 (V)           |

| Total no. of pixels:  | 1072 (H) x 1030 (V)           |

| Optical black pixels: | Left: 20 Right: 20            |

| Timing pixels:        | Left: 4 Right: 4              |

| Dummy register cells: | Left: 7 Right: 7              |

| Optical black lines:  | Bottom: 6 Top: 6              |

|                       |                               |

Figure 1 - Device structure

#### FTT1010-M

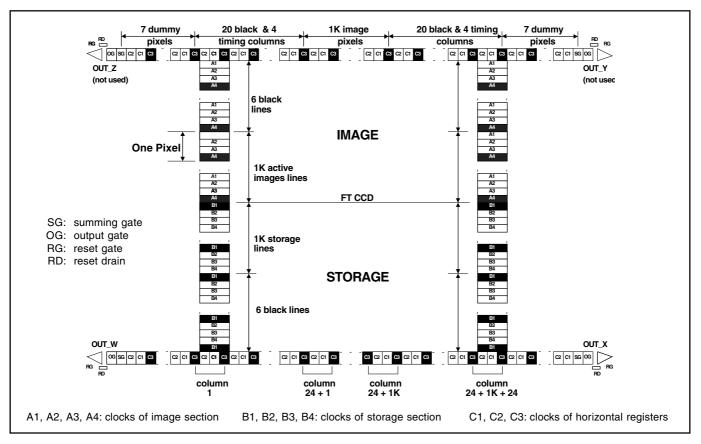

#### Architecture of the FTT1010-M

The FTT1010-M consists of a shielded storage section and an open image section. Both sections are electronically the same and have the same cell structure with the same properties. The only difference between the two sections is the optical light shield.

The optical centres of all pixels in the image section form a square grid. The charge is generated and integrated in this section. Output registers are located below the storage section. The output amplifiers Y and Z are not used in Frame Transfer mode and should be connected as not-used amplifiers.

After the integration time the charge collected in the image section is shifted to the storage section. The charge is read out line by line through the lower output register. The left and the right half of each output register can be controlled independently. This enables either single or multiple read-out.

During vertical transport the C3 gates separate the pixels in the register. The letters W, X, Y and Z are used to define the four quadrants of the sensor. The central C3 gates of both registers are part of the W and Z quadrants of the sensor.

Both upper and lower registers can be used for vertical binning. Both registers also have a summing gate at each end that can be used for horizontal binning. Figure 2 shows the detailed internal structure.

#### IMAGE SECTION

Image diagonal (active video only) 17.38 mm Aspect ratio 1:1 Active image width x height 12.288 x 12.288 mm<sup>2</sup> Pixel width x height 12x12 µm<sup>2</sup> Geometric fill factor 100% Image clock pins A1, A2, A3, A4 Capacity of each clock phase 2.5nF per pin Number of active lines 1024 Number of black reference lines 2 Number of dummy black lines 4 Total number of lines 1030 Number of active pixels per line 1024 Number of overscan (timing) pixels per line 8 (2x4) Number of black reference pixels per line 40 (2x20) Total number of pixels per line 1072

| STORAGE SECTION                                                                                                                                      |                                                                                                             |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| Storage width x height<br>Cell width x height<br>Storage clock phases<br>Capacity of each clock phase<br>Number of cells per line<br>Number of lines | 12.864 x 12.360 mm <sup>2</sup><br>12x12 μm <sup>2</sup><br>B1, B2, B3, B4<br>2.5nF per pin<br>1072<br>1030 |  |

|                                                 | OUTPUT REGISTERS         |  |  |

|-------------------------------------------------|--------------------------|--|--|

| Output buffers (three-stage source follower)    | 4 (one on each corner)   |  |  |

| Number of registers                             | 2 (one above, one below) |  |  |

| Number of dummy cells per register              | 14 (2x7)                 |  |  |

| Number of register cells per register           | 1072                     |  |  |

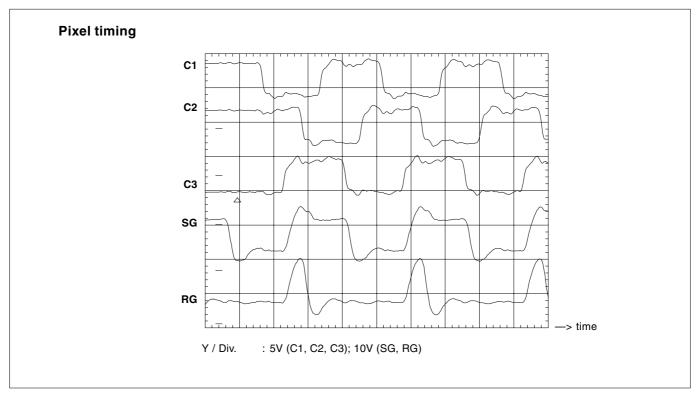

| Output register horizontal transport clock pins | C1, C2, C3               |  |  |

| Capacity of each C-clock phase                  | 60pF per pin             |  |  |

| Overlap capacity between neighbouring C-clocks  | 20pF                     |  |  |

| Output register Summing Gates                   | 4 pins (SG)              |  |  |

| Capacity of each SG                             | 15pF                     |  |  |

| Reset Gate clock phases                         | 4 pins (RG)              |  |  |

| Capacity of each RG                             | 15pF                     |  |  |

Figure 2 - Detailed internal structure

## FTT1010-M

#### Specifications

| ABSOLUTE MAXIMUM RATINGS <sup>1</sup>                                                                                                                                                                        | MIN.                           | MAX.                            | UNIT                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------|---------------------------|

| GENERAL:<br>storage temperature<br>ambient temperature during operation<br>voltage between any two gates<br>DC current through any clock phase (absolute value)<br>OUT current (no short circuit protection) | -55<br>-40<br>-20<br>-0.2<br>0 | +80<br>+60<br>+20<br>+2.0<br>10 | °C<br>°C<br>V<br>μA<br>mA |

| VOLTAGES IN RELATION TO VPS:<br>VNS, SFD, RD<br>VCS, SFS<br>all other pins                                                                                                                                   | -0.5<br>-8<br>-5               | +30<br>+5<br>+25                | V<br>V<br>V               |

| VOLTAGES IN RELATION TO VNS:<br>SFD, RD<br>VCS, SFS, VPS<br>all other pins                                                                                                                                   | -15<br>-30<br>-30              | +0.5<br>+0.5<br>+0.5            | V<br>V<br>V               |

|                  | DC CONDITIONS <sup>2</sup> | MIN. [V] | TYPICAL [V] | MAX. [V] | MAX. [mA] |

|------------------|----------------------------|----------|-------------|----------|-----------|

| VNS <sup>³</sup> | N substrate                | 18       | 24          | 28       | 15        |

| VPS              | P substrate                | 1        | 3           | 7        | 15        |

| SFD              | Source Follower Drain      | 16       | 20          | 24       | 4.5       |

| SFS              | Source Follower Source     | _        | 0           | -        | 1         |

| VCS              | Current Source             | -5       | 0           | 3        | -         |

| OG               | Output Gate                | 4        | 6           | 8        | -         |

| RD               | Reset Drain                | 13       | 15.5        | 18       | -         |

| AC CLOCK LEVEL CONDITIONS <sup>2</sup>                                                                                                                                                                              | MIN.          | TYPICAL               | MAX.       | UNIT             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------|------------|------------------|

| IMAGE CLOCKS:<br>A-clock amplitude during integration and hold<br>A-clock amplitude during vertical transport (duty cycle=5/8) <sup>4</sup><br>A-clock low level<br>Charge Reset (CR) level on A-clock <sup>5</sup> | 8<br>10<br>-5 | 10<br>14<br>0<br>-5   |            | V<br>V<br>V<br>V |

| STORAGE CLOCKS:<br>B-clock amplitude during hold<br>B-clock amplitude during vertical transport (duty cycle=5/8)                                                                                                    | 8<br>10       | 10<br>14              |            | V<br>V           |

| OUTPUT REGISTER CLOCKS:<br>C-clock amplitude (duty cycle during hor. transport = 3/6)<br>C-clock low level<br>Summing Gate (SG) amplitude<br>Summing Gate (SG) low level                                            | 4.75<br>2     | 5<br>3.5<br>10<br>3.5 | 5.25<br>10 | V<br>V<br>V<br>V |

| OTHER CLOCKS:<br>Reset Gate (RG) amplitude<br>Reset Gate (RG) low level<br>Charge Reset (CR) pulse on Nsub <sup>₅</sup>                                                                                             | 5<br>0        | 10<br>3<br>10         | 10<br>10   | V<br>V<br>V      |

<sup>1</sup> During Charge Reset it is allowed to exceed maximum rating levels (see note<sup>5</sup>).

<sup>2</sup> All voltages in relation to SFS.

<sup>3</sup> To set the VNS voltage for optimal Vertical Anti-Blooming (VAB), it should be adjustable between minimum and maximum values.

<sup>4</sup> Three-level clock is preferred for maximum charge; the swing during vertical transport should be 4V higher than the voltage during integration. A two level clock (typically 10V) can be used if a lower maximum charge handling capacity is allowed.

<sup>5</sup>Charge Reset can be achieved in two ways:

• The typical CR level is applied to all image clocks simultaneously (preferred).

• The typical A-clock low level is applied to all image clocks; for proper CR, an additional Charge Reset pulse on VNS is required. This will also affect the charge handling capacity in the storage areas.

#### FTT1010-M

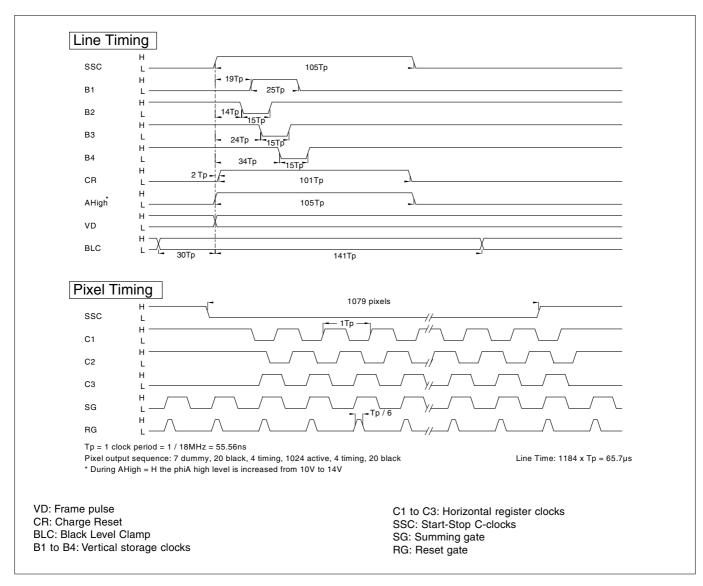

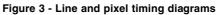

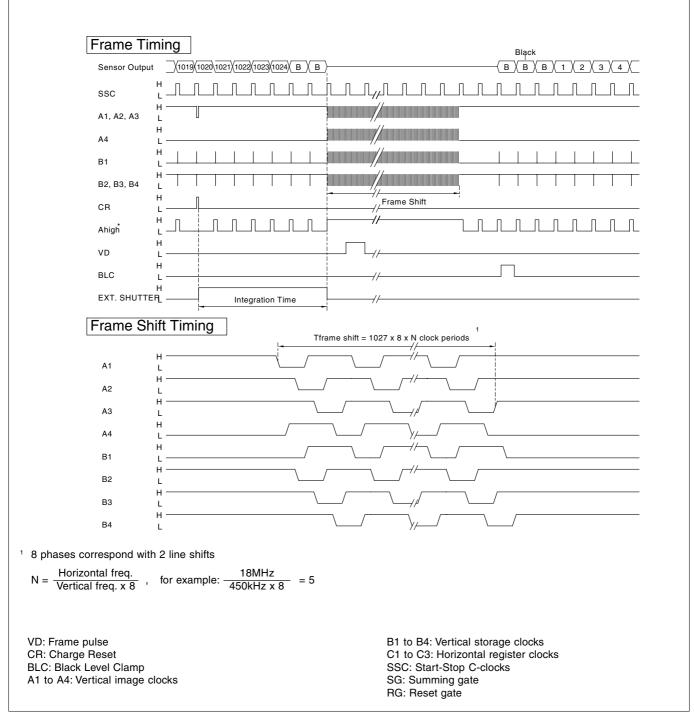

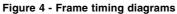

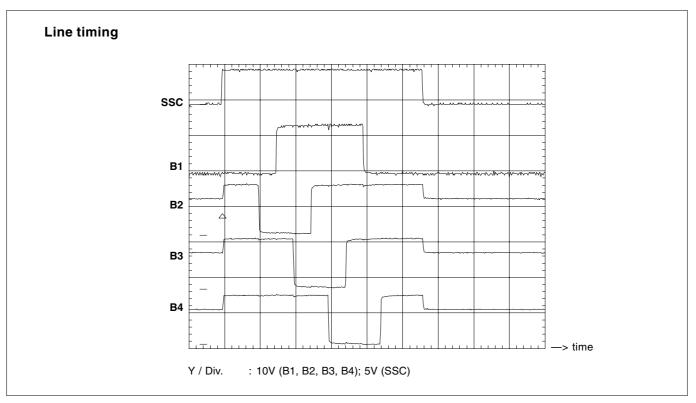

#### Timing diagrams (for default operation)

| MIN. | TYPICAL                      | MAX.                                         | UNIT                                                                                                                                                                                                              |

|------|------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 18                           | 40                                           | MHz                                                                                                                                                                                                               |

| 0    | 450                          | 1000                                         | kHz                                                                                                                                                                                                               |

| 2    | 5                            |                                              | μs                                                                                                                                                                                                                |

| 10   | 20                           |                                              | ns                                                                                                                                                                                                                |

| 10   | 20                           |                                              | ns                                                                                                                                                                                                                |

| 3    | 5                            | 1/6 Tp                                       | ns                                                                                                                                                                                                                |

| 3    | 5                            | 1/6 Tp                                       | ns                                                                                                                                                                                                                |

| 3    | 5                            | 1/6 Tp                                       | ns                                                                                                                                                                                                                |

|      | 0<br>2<br>10<br>10<br>3<br>3 | 0 450<br>2 5<br>10 20<br>10 20<br>3 5<br>3 5 | 0         450         1000           2         5         1000           10         20         1000           10         20         1000           3         5         1/6 Tp           3         5         1/6 Tp |

$^{1}$ Tp = 1 clock period

$^{2}$  Duty cycle = 50% and phase shift of the C clocks is 120 degrees.

Figure 5 - Vertical readout

Figure 6 - Start horizontal readout

# FTT1010-M

#### Performance

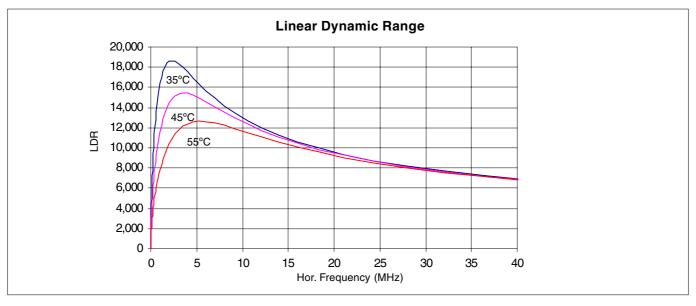

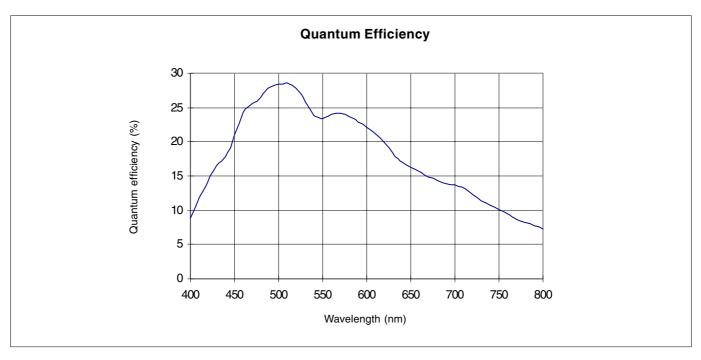

The test conditions for the performance characteristics are as follows:

- All values are measured using typical operating conditions.

VNS is adjusted as low as possible while maintaining proper

- Vertical Anti-Blooming.

- Sensor temperature = 60°C (333K).

- Horizontal transport frequency = 18MHz.

- Vertical transport frequency = 450kHz (unless specified otherwise).

- Integration time = 10ms (unless specified otherwise).

- The light source is a 3200K lamp with neutral density filters and a 1.7mm thick BG40 infrared cut-off filter. For Linear Operation measurements, a temperature conversion filter (Melles Griot type no. 03FCG261, -120 mired, thickness: 2.5mm) is applied.

| LINEAR OPERATION                                   | MIN.   | TYPICAL  | MAX. | UNIT      |

|----------------------------------------------------|--------|----------|------|-----------|

| Linear dynamic range <sup>1</sup>                  | 4200:1 |          |      |           |

| Charge Transfer Efficiency <sup>2</sup> vertical   |        | 0.999995 |      |           |

| Charge Transfer Efficiency <sup>2</sup> horizontal |        | 0.999999 |      |           |

| Image lag                                          |        |          | 0    | %         |

| Smear <sup>3</sup>                                 |        | -39      | 0    | dB        |

| Resolution (MTF) @ 42 lp/mm                        | 65     |          |      | %         |

| Responsivity                                       | 180    | 250      |      | kel/lux⋅s |

| Quantum efficiency @ 530 nm                        | 25     | 30       |      | %         |

| White Shading <sup>₄</sup>                         |        |          | 2.5  | %         |

| Random Non-Uniformity (RNU) <sup>₅</sup>           |        | 0.3      | 5    | %         |

| VNS required for good Vertical Anti-Blooming (VAB) | 18     | 24       | 28   | V         |

| Power dissipation at 15 frames/s                   |        | 410      |      | mW        |

<sup>1</sup> Linear dynamic range is defined as the ratio of Q in to read-out noise (the latter reduced by Correlated Double Sampling).

<sup>2</sup> Charge Transfer Efficiency values are tested by evaluation and expressed as the value per gate transfer.

<sup>3</sup> Smear is defined as the ratio of 10% of the vertical transport time to the integration time. It indicates how visible a spot of 10% of the image height would become.

<sup>4</sup> White Shading is defined as the ratio of the one-σ value of the pixel output distribution expressed as a percentage of the mean value output (low pass image).

<sup>5</sup> RNU is defined as the ratio of the one- $\sigma$  value of the highpass image to the mean signal value at nominal light.

Figure 7 - Typical Linear dynamic range vs. horizontal read-out frequency and sensor temperature

Figure 8 - Maximum number of images/second versus integration time

Figure 9 - Quantum efficiency versus wavelength

## FTT1010-M

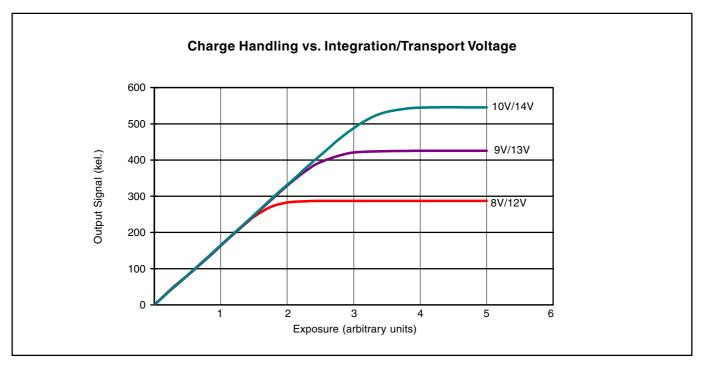

| LINEAR/SATURATION                                       | MIN. | TYPICAL | MAX. | UNIT        |

|---------------------------------------------------------|------|---------|------|-------------|

| Full-well capacity saturation level (Qmax) <sup>1</sup> | 250  | 500     | 600  | kel.        |

| Full-well capacity shading (Qmax, shading) <sup>2</sup> | 200  | 10      | 50   | %           |

| Full-well capacity linear operation (Qlin) <sup>3</sup> | 200  | 350     |      | kel.        |

| Charge handling capacity 4                              |      | 600     |      | kel.        |

| Overexposure <sup>5</sup> handling                      | 100  | 200     |      | x Qmax leve |

| Overexposure ° handling                                 | 100  | 200     |      | x Qmax      |

<sup>1</sup>Qmax is determined from the lowpass filtered image.

<sup>2</sup> Qmax, shading is the maximum difference of the full-well charges of all pixels, relative to Qmax.

<sup>3</sup> The linear full-well capacity Qlin is calculated from linearity test (see dynamic range). The evaluation test guarantees 97% linearity.

<sup>4</sup> Charge handling capacity is the largest charge packet that can be transported through the register and read-out through the output buffer.

<sup>5</sup>Overexposure over entire area while maintaining good Vertical Anti-Blooming (VAB). It is tested by measuring the dark line.

Figure 10 - Charge handling versus integration/transport voltage

# FTT1010-M

| OUTPUT BUFFERS                                                           | MIN. | TYPICAL | MAX. | UNIT   |

|--------------------------------------------------------------------------|------|---------|------|--------|

| Conversion factor                                                        | 6    | 0       | 12   | μV/el. |

|                                                                          | 6    | 8       |      | •      |

| Mutual conversion factor matching $(\Delta ACF)^1$                       |      | 0       | 2    | μV/el. |

| Supply current                                                           |      | 4       |      | mA     |

| Bandwidth                                                                |      | 110     |      | MHz    |

| Output impedance buffer ( $R_{load} = 3.3 k\Omega$ , $C_{load} = 2 pF$ ) |      | 400     |      | Ω      |

<sup>1</sup> Matching of the four outputs is specified as  $\Delta$ ACF with respect to reference measured at the operating point (Q<sub>iin</sub>/2).

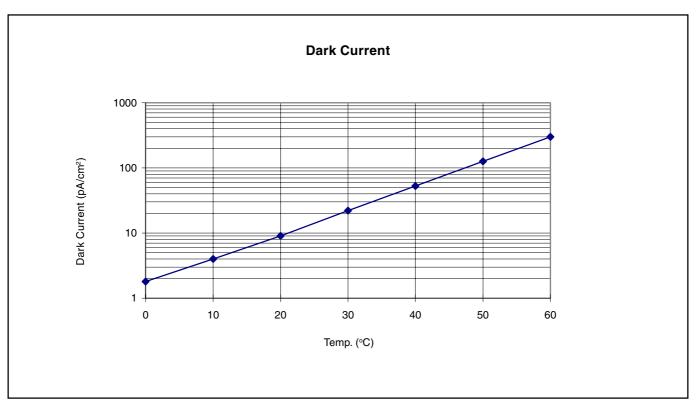

| DARK CONDITION                               | MIN. | TYPICAL | MAX. | UNIT               |

|----------------------------------------------|------|---------|------|--------------------|

| Dark current level @ 30° C                   |      | 20      | 30   | pA/cm <sup>2</sup> |

| Dark current level @ 60° C                   |      | 0.3     | 0.6  | nA/cm²             |

| Fixed Pattern Noise 1 (FPN) @ 60° C          |      | 15      | 25   | el.                |

| RMS readout noise @ 9MHz bandwidth after CDS |      | 25      | 30   | el.                |

$^{1}\,\text{FPN}$  is the one- $\sigma$  value of the highpass image.

Figure 11 - Dark current versus temperature

#### FTT1010-M

#### **Application information**

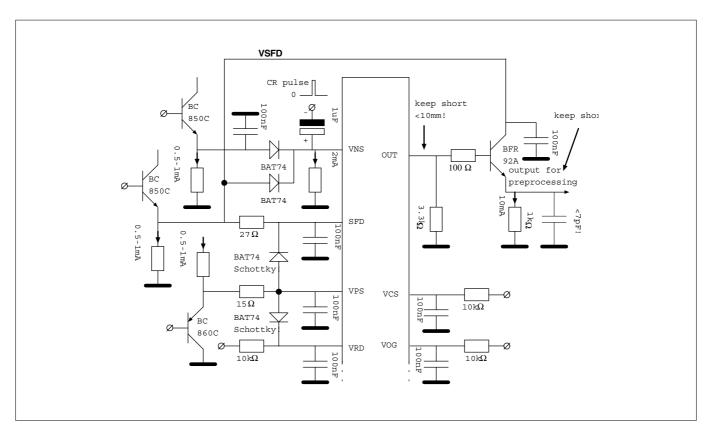

#### Current handling

One of the purposes of VPS is to drain the holes that are generated during exposure of the sensor to light. Free electrons are either transported to the VRD connection and, if excessive (from over-exposure), free electrons are drained to VNS. No current should flow into any VPS connection of the sensor. During high overexposure a total current 10 to 15mA through all VPS connections together may be expected. The PNP emitter follower in the circuit diagram (figure 12) serves these current requirements.

VNS drains superfluous electrons as a result of overexposure. In other words, it only sinks current. During high overexposure a total current of 10 to 15mA through all VNS connections together may be expected. The NPN emitter follower in the circuit diagram meets these current requirements. The clamp circuit, consisting of the diode and electrolytic capacitor, enables the addition of a Charge Reset (CR) pulse on top of an otherwise stable VNS voltage. To protect the CCD, the current resulting from this pulse should be limited. This can be accomplished by designing a pulse generator with a rather high output impedance.

#### Decoupling of DC voltages

All DC voltages (not VNS, which has additional CR pulses as described above) should be decoupled with a 100nF decoupling capacitor. This capacitor must be mounted as close as possible to the sensor pin. Further noise reduction (by bandwidth limiting) is achieved by the resistors in the connections between the sensor and its voltage supplies. The electrons that build up the charge packets that will reach the floating diffusions only add up to a small current, which will flow through VRD. Therefore a large series resistor in the VRD connection may be used.

#### Outputs

To limit the on-chip power dissipation, the output buffers are designed with open source outputs. Outputs to be used should therefore be loaded with a current source or more simply with a resistance to GND. In order to prevent the output (which typically has an output impedance of about  $400\Omega$ ) from bandwidth limitation as a result of capacitive loading, load the output with an emitter follower built from a high-frequency transistor. Mount the base of this transistor as close as possible to the sensor and keep the connection between the emitter and the next stage short.

The CCD output buffer can easily be destroyed by ESD. By using this emitter follower, this danger is suppressed; do NOT reintroduce this danger by measuring directly on the output pin of the sensor with an oscilloscope probe. Instead, measure on the output of the emitter follower. Slew rate limitation is avoided by avoiding a toosmall quiescent current in the emitter follower; about 10mA should do the job. The collector of the emitter follower should be decoupled properly to suppress the Miller effect from the base-collector capacitance.

A CCD output load resistor of  $3.3k\Omega$  typically results in a bandwidth of 110MHz. The bandwidth can be enlarged to about 130MHz by using a resistor of  $2.2k\Omega$  instead, which, however, also enlarges the on-chip power dissipation.

#### Device protection

The output buffers of the FTT1010-M are likely to be damaged if VPS rises above SFD or RD at any time. This danger is most realistic during power-on or power-off of the camera. The RD voltage should always be lower than the SFD voltage.

Never exceed the maximum output current. This may damage the device permanently. The maximum output current should be limited to 10mA. Be especially aware that the output buffers of these image sensors are very sensitive to ESD damage.

Because of the fact that our CCDs are built on an n-type substrate, we are dealing with some parasitic npn transistors. To avoid activation of these transistors during switch-on and switch-off of the camera, we recommend the application diagram of figure 12.

#### Unused sections

To reduce power consumption the following steps can be taken. Connect unused output register pins (C1...C3, SG, OG) and unused SFS pins to zero Volts.

#### More information

Detailed application information is provided in the application note AN01 entitled '**Camera Electronics for the mK x nK CCD Image Sensor Family**'.

#### FTT1010-M

#### **Device Handling**

An image sensor is a MOS device which can be destroyed by electrostatic discharge (ESD). Therefore, the device should be handled with care.

Always store the device with short-circuiting clamps or on conductive foam. Always switch off all electric signals when inserting or removing the sensor into or from a camera (the ESD protection in the CCD image sensor process is less effective than the ESD protection of standard CMOS circuits).

Being a high quality optical device, it is important that the cover glass remain undamaged. When handling the sensor, use fingercots.

When cleaning the glass we recommend using ethanol (or possibly water). Use of other liquids is strongly discouraged:

- if the cleaning liquid evaporates too quickly, rubbing is likely to cause ESD damage.

- the cover glass and its coating can be damaged by other liquids.

Rub the window carefully and slowly.

Dry rubbing of the window may cause electro-static charges or scratches which can destroy the device.

Figure 12 - Application diagram to protect the FTT1010-M

#### FTT1010-M

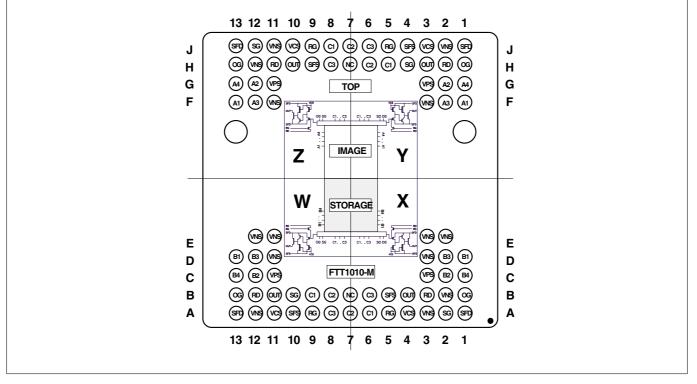

#### **Pin configuration**

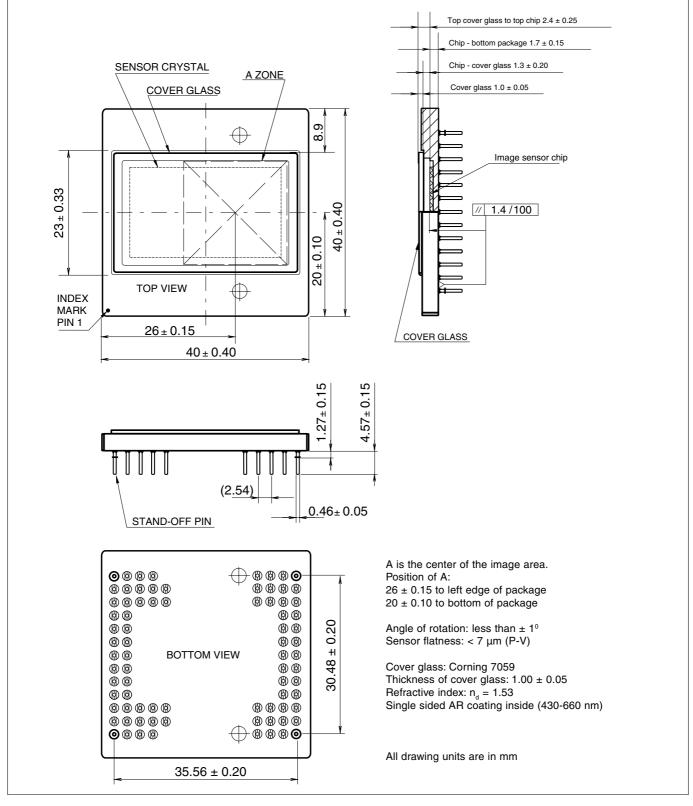

The FTT1010-M is mounted in a Pin Grid Array (PGA) package with 76 pins in a 15x13 grid of  $40.00 \times 40.00$  mm<sup>2</sup>. The position of pin A1 is marked with a gold dot on top of the package.

The clock phases of quadrant W are internally connected to X, and the clock phases of Y are connected to Z.

| Symbol | Name                     | Pin # W | Pin # X | Pin # Y | Pin # Z |

|--------|--------------------------|---------|---------|---------|---------|

| VNS    | N substrate              | A12     | A3      | J2      | F11     |

| VNS    | N substrate              | D11     | B2      | F3      | H12     |

| VNS    | N substrate              | E11     | D3      | -       | J11     |

| VNS    | N substrate              | E12     | E2      | -       | -       |

| VNS    | N substrate              | -       | E3      | -       | -       |

| VPS    | P substrate              | C11     | C3      | G3      | G11     |

| SFD    | Source Follower Drain    | A13     | A1      | J1      | J13     |

| SFS    | Source Follower Source   | A10     | B5      | J4      | H9      |

| VCS    | Current Source           | A11     | A4      | J3      | J10     |

| OG     | Output Gate              | B13     | B1      | H1      | H13     |

| RD     | Reset Drain              | B12     | B3      | H2      | H11     |

| A1     | Image Clock (Phase 1)    | -       | -       | F1      | F13     |

| A2     | Image Clock (Phase 2)    | -       | -       | G2      | G12     |

| A3     | Image Clock (Phase 3)    | -       | -       | F2      | F12     |

| A4     | Image Clock (Phase 4)    | -       | -       | G1      | G13     |

| B1     | Storage Clock (Phase 1)  | D13     | D1      | -       | -       |

| B2     | Storage Clock (Phase 2)  | C12     | C2      | -       | -       |

| B3     | Storage Clock (Phase 3)  | D12     | D2      | -       | -       |

| B4     | Storage Clock (Phase 4)  | C13     | C1      | -       | -       |

| C1     | Register Clock (Phase 1) | B9      | A6      | H5      | J8      |

| C2     | Register Clock (Phase 2) | B8      | A7      | H6      | J7      |

| C3     | Register Clock (Phase 3) | A8      | B6      | J6      | H8      |

| SG     | Summing Gate             | B10     | A2      | H4      | J12     |

| RG     | Reset Gate               | A9      | A5      | J5      | J9      |

| OUT    | Output                   | B11     | B4      | H3      | H10     |

| NC     | Not connected            | B7      |         | H7      |         |

|        |                          |         |         |         |         |

Figure 13 - FTT1010-M pin configuration (top view)

## FTT1010-M

## Frame Transfer CCD Image Sensor

#### Package information

Figure 14 - Mechanical drawing of the PGA package of the FTT1010-M

#### Order codes

The sensors can be ordered using the following codes:

| FTT1010-M sensors |                  |                |

|-------------------|------------------|----------------|

| Description       | Quality Grade    | Order Code     |

| FTT1010-M/TG      | Test grade       | 9922 157 35031 |

| FTT1010-M/EG      | Economy grade    | 9922 157 35051 |

| FTT1010-M/IG      | Industrial grade | 9922 157 35021 |

| FTT1010-M/HG      | High grade       | 9922 157 35011 |

You can contact the Image Sensors division of DALSA at the following address:

DALSA Professional Imaging Prof. Holstlaan 4 (WZ08) 5656 AA Eindhoven The Netherlands

phone +31 - 40 - 27 45 600 fax +31 - 40 - 27 44 090

www.dalsa.com